2024, 30(5), 12904-12909

ISSN: 2148-2403 https://kuey.net/

**Research Article**

## Design And Validation Of A 32-Bit RISC-V Processor Incorporating Vedic Mathematics

Dr. Girish H<sup>1\*</sup>, Shylaja V<sup>2</sup>, Dr. Vijayalakshmi D<sup>3</sup>, Vanishree M L<sup>4</sup>, Soumya N G <sup>5</sup>, Dr. Anita P<sup>6</sup>

- $^{\scriptscriptstyle 1}$ Professor, Department of Electronics and Communication Engineering, Cambridge Institute of Technology, Bengaluru, India, hgirishphd@gmail.com

- <sup>2</sup>Assistant professor, Department of Electronics and Communication Engineering, Bangalore Institute of Technology, Bangalore. shylajav@bit-bangalore.edu.in

- <sup>3</sup>Associate professor, Department of Electronics and Communication Engineering, Bangalore Institute of Technology, Bangalore. lakshmi@bit-bangalore.edu.in

- <sup>4</sup>Assistant professor, Department of CSE, Global Academy of Technology, Bengaluru vanishree.ml@gat.ac.in

- <sup>5</sup>Assistant professor, Department of CSE, R N S Institute of Technology, Bengaluru. soumya.ng21@gmail.com

- <sup>6</sup>Assistant professor, Department of Electronics and Communication Engineering, KSIT, Bangalore. anitsp2002@gmail.com

Citation: Dr. Girish H.et al (2024), Design And Validation Of A 32-Bit RISC-V Processor Incorporating Vedic Mathematics, *Educational Administration: Theory and Practice*, 30(5), 12904-12909, Doi: 10.53555/kuey.v30i5.4465

### ARTICLE INFO ABSTRACT

A Vedic multiplier architecture is employed in constructing a 32-bit RISC-V processor to enhance speed and reduce computational complexity. It's ALU and MAC units, based on Vedic Sutras, are implemented in Verilog HDL and simulated with the Xilinx design suite, achieving lower power consumption and latency compared to traditional designs. The processor includes conventional components like the Control Unit, Register Bank, Program Counter, and Memory. It can execute up to 16 instructions, making it a powerful option for various computing tasks due to its improved speed, reduced power consumption, and minimized area usage.

**Keywords:** Reduced Instruction Set Computer, RISC V, Von Neumann architecture, Verilog HDL, Vedic Mathematics, Urdhva-Tiryagbhyam Sutra.

#### **INTRODUCTION:**

The RISC-V architecture prioritizes simple instruction sets, enhancing efficient decoding and often resulting in better performance than CISC. This approach, combining straightforward instructions with a microprocessor architecture capable of executing instructions within a few cycles, offers fixed instruction sizes, additional registers, and superior clock utilization, albeit with potentially higher memory and code requirements. Performance gains are typically two to four times greater than those of CISC processors. Designing a 32-bit RISC-V processor using Hardware Description Language involves integrating internal components such as registers, ALUs, memory units, and control units, and can be effectively implemented on FPGA.

Vedic mathematics, using techniques known as sutras, provides rapid solutions to mathematical problems, proving effective within mainstream mathematics rather than as a separate discipline. Multipliers, crucial in processors, especially in digital signal processing and communication (e.g., FFT), benefit from Vedic mathematics. Low power consumption is targeted for logarithmic multipliers, addressing drawbacks in common binary multiplication techniques like array and Booth multiplication. Vedic multipliers, based on the Urdhva Triyagbhyam Sutra, offer efficient alternatives, with research demonstrating their superiority in terms of area, power, and delays compared to traditional methods. High-speed Vedic multipliers enhance DSP operations, facilitating quick calculations.

Reversible circuits further reduce power usage compared to combinational logic circuits, and RTL circuit verification is conducted using property-driven verification. In DSP applications, where multiplication often involves repetitive addition, the Ekadhikena Purvena Sutra simplifies the squaring task. Multipliers generally follow a three-step process: partial product generation (PPG), partial product reduction (PPR), and final addition, with AND gates generating a partial product matrix (PPM) during the PPG stage for unsigned multiplication.

#### LITERATURE REVIEW:

In "Design and Comparison of Multiplier using Vedic Sutras" by S. Lad and V. S. Bendre, presented at the 2019 5th International Conference On Computing, Communication, Control And Automation (ICCUBEA), the authors highlight the crucial role of rapid processing units in contemporary computational tasks, particularly for real-time applications. These units, featuring Arithmetic Logic Units (ALUs) and Multiply-Accumulate (MAC) units, depend heavily on efficient multipliers to enhance execution speed and accuracy in digital signal processors. Optimization of these components—multipliers, adders, and registers—is essential for performance improvement.

The design and verification of a 16-bit RISC processor by Seung Pyo Jung et al., detailed at the 2008 International SoC Design Conference in Busan, introduces a processor with Harvard architecture, a 24-bit address, and a 5-stage pipeline. This processor, implemented on FPGA, successfully runs the ADPCM vocoder and SOLA algorithm. The need for compact, low-power processors in portable multimedia players (PMPs) and personal digital assistants (PDAs) is addressed by this design, which aims for SOC-level ASIC integration. Despite the widespread use of 8051 and ARM 7 processors, they present limitations in size and calculation time, prompting the development of this new 16-bit RISC processor.

In "Design and Implementation of 16 Bit Processor on FPGA," Balpande Vishwas V et al. describe the creation of a 16-bit RISC processor using Verilog HDL and Harvard architecture. The project ensures a simple instruction set for seamless hardware execution, modeling complex components like the ALU and memory behaviorally, while simpler components like adders are approached structurally. The processor's functionality is verified through simulation, allowing for future expansion to 32 or 64-bit processors with minor code modifications.

F. Adamec and T. Fryza's "Design — Time configurable processor basic structure," presented at the 13th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems, introduces a time-configurable processor core, emphasizing its minimal integer core configuration. The project compares this design with similar solutions, such as the Xtensa processor from Tensilica, which offers extendable instruction sets and advanced features like FPU, DSP engines, and multimedia codec acceleration. The Xtensa architecture follows a RISC LOAD/STORE approach and supports VLIW execution, demonstrating flexibility for various computational demands.

#### **METHODOLOGY:**

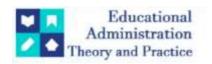

Fig 1: Block diagram of processor

The multiplier unit is an essential component in any processor, forming the foundation for high-speed design techniques as detailed in [13][14]. The Urdhva Tiryagbhyam method was developed for efficient mental calculations by multiplying each row, introducing vertical and crosswise addition and multiplication, and using a straightforward digit from each unit for easy recall.

The Arithmetic Logic Unit (ALU) in a combinational circuit performs various bitwise and arithmetic operations using a set of instructions. In a CPU, the ALU receives an instruction and operands, with the opcode determining the operation to be performed on the operands.

The Control Unit generates control signals to manage resources such as registers and external memory, and to dictate the tasks they perform. In our system, the Control Unit sends control signals to the memory and register blocks for reading or writing data and manages the branching signals based on instruction execution.

The register block contains 32 registers that can store and write 32-bit values from the memory block or ALU in response to control signals. Each register is accessible via a unique address within the memory block.

The memory block serves as external memory, storing 32-bit addressable words. The ALU can read from and write to this block in response to control signals.

The instruction block stores the set of instructions to be executed, while the program counter holds the address of the current instruction. The program counter increments with each clock cycle, pointing to the next instruction's address.

The instruction decoder identifies the type of instruction from the processor's instruction library and assigns the appropriate registers to each part of the instruction. Based on the opcode, it decodes the instruction into various locations and function values.

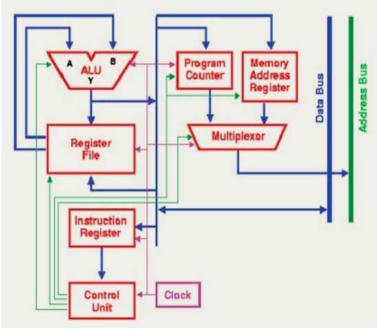

Fig 2: Gate level Netlist

RISC-V Processor Core: Begin by establishing the essential components of a RISC-V processor core, which include the instruction fetch, decode, execute, memory access, and write-back stages. Vedic Multiplier Integration: Integrate the Vedic multiplier into the execution stage of the processor pipeline, adding components that efficiently multiply two operands using Vedic multiplication techniques. Incorporate pipeline registers between stages to ensure the seamless flow of instructions and data throughout the processor pipeline. Design control logic to manage the flow of instructions and data, addressing hazards, stall conditions, and branching effectively. Develop interfaces for accessing instruction and data memory, encompassing the instruction cache, data cache, and main memory.

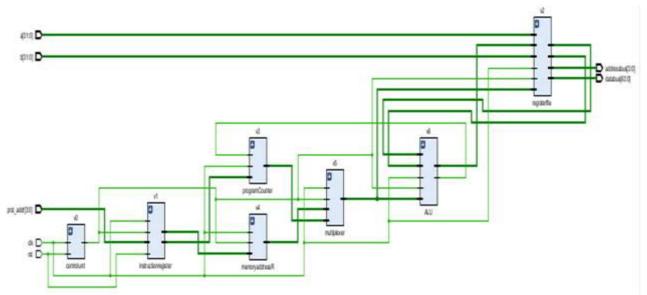

Fig 3: RTL Schematic

This schematic integrates the RISC-V processor's core components with the Vedic multi plier allowing for faster and more precise arithmetic calculations. The 32-bit RISC-V processor featuring a Vedic multiplier utilizes a simplified instruction set architecture (RISC) to perform computations efficiently. The Vedic multiplier, based on ancient Indian mathematics, enhances multiplication operations by breaking them down into smaller, more manageable steps. This schematic integrates the RISC-V processor's core components with the Vedic multiplier.

#

#### **RESULT:**

Fig 4: Simulation Results

The waveform output for a 32-bit RISC-V processor utilizing the Vedic multiplier would depict various stages of the processor's operation over time. This includes signals representing instruction fetch, decode, execution, memory access, and write-back stages. Additionally, specific signals related to the Vedic multiplier, such as partial products generation, addition, and accumulation, would be visible. The waveform would showcase the efficient parallel processing capabilities of the Vedic multiplier, resulting in faster multiplication operations compared to traditional methods.

|           | Area (LUT's) | Delay (ns) |

|-----------|--------------|------------|

| processor | 3795         | 64.549     |

Fig 5: Evaluation of Area and delay report

#### **CONCLUSION:**

This paper details the implementation of a RISC-V processor with an ALU based on Vedic sutras. By using Vedic multipliers, the design enhances multiplication speed while reducing the size and power requirements

of the multipliers. The Vedic processor incorporates standard processor blocks along with Vedic MAC and Vedic ALU units. The architecture supports a 14-instruction set. The performance of the Vedic ALU and MAC is compared with current ALU and MAC results, demonstrating that the 32-bit Vedic processor significantly reduces latency and conserves energy compared to traditional processors. Key features of the RISC-V CPU design include higher operating speed, lower power consumption, and decreased area usage.

#### **REFERENCES:**

- 1. S. Lad and V. S. Bendre, "Design and Comparison of Multiplier using Vedic Sutras," 2019 5th International Conference on Computing, Communication, Control and Automation (ICCUBEA), Pune, India, 2019, pp. 1-5.

- 2. Balpande Vishwas V, Abhishek B. Pande, Meeta J. Walke, Bhavna D. Choudhari and Kiran R. Bagade. "Design and Implementation of 16 Bit Processor on FPGA." (2015)

- 3. Seung Pyo Jung, Jingzhi Xu, Dong-Hoon Lee, Ju Sung Park, Kang-Joo Kim, and Koon-Shik Cho, "Design & verification of 16-bit RISC processor," 2008 International SoC Design Conference, Busan, 2008, pp. III-13-III-14, Doi: 10.1109/SOCDC.2008.4815726.

- 4. F. Adamec and T. Feyza, "Design Time configurable processor basic structure," 13th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems, Vienna, 2010, pp. 119-120, Doi: 10.1109/DDECS.2010.5491804.

- 5. A. Bisoyi, M. Baral and M. K. Senapati, "Comparison of a 32-bit Vedic multiplier with a conventional binary multiplier," 2014 IEEE International Conference on Advanced Communications, Control and Computing Technologies, Padmanabhapuram, 2014, pp. 1757- 1760, Doi: 10.1109/ICACCCT.2014.7019410.

- 6. H. Girish, T. G. Manjunat and A. C. Vikramathithan, "Detection and Alerting Animals in Forest using Artificial Intelligence and IoT," 2022 IEEE Fourth International Conference on Advances in Electronics, Computers and Communications (ICAECC), 2022, pp. 1-5, doi: 10.1109/ICAECC54045.2022.9716679.

- 7. A. Devipriya, H. Girish, V. Srinivas, N. Adi Reddy and D. Rajkiran, "RTL Design and Logic Synthesis of Traffic Light Controller for 45nm Technology," 2022 3rd International Conference for Emerging Technology (INCET), 2022, pp. 1-5, doi: 10.1109/INCET54531.2022.9824833.

- 8. S. Vaddadi, V. Srinivas, N. A. Reddy, G. H, R. D and A. Devipriya, "Factory Inventory Automation using Industry 4.0 Technologies," 2022 IEEE IAS Global Conference on Emerging Technologies (GlobConET), 2022, pp. 734-738, doi: 10.1109/GlobConET53749.2022.9872416.

- 9. T G Manjunath, A C Vikramathithan, H Girish, "Analysis of Total Harmonic Distortion and implementation of Inverter Fault Diagnosis using Artificial Neural Network", Journal of Physics: Conference Series, Volume 2161, 1st International Conference on Artificial Intelligence, Computational Electronics and Communication System (AICECS 2021) 28-30 October 2021, Manipal, India. https://iopscience.iop.org/issue/1742-6596/2161/1

- 10. GIRISH H , "Internet of Things Based Heart Beat Rate Monitoring System", © September 2022 | IJIRT | Volume 6 Issue 4 | ISSN: 2349-6002 IJIRT 156592 INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN TECHNOLOGY 227

- 11. Dr Girish H, Dr. Mangala Gowri , Dr. Keshava Murthy , Chetan Naik J, Autonomous Car Using Deep Learning and Open CV, PAGE NO: 107-115, VOLUME 8 ISSUE 10 2022, Gradiva review journal, ISSN NO: 0363-8057, DOI:10.37897.GRJ.2022.V8I8.22.50332

- 12. Girish H. "Intelligent Traffic Tracking System Using Wi-Fi ." International Journal for Scientific Research and Development 8.12 (2021): 86-90.

- 13. Girish H, Shashikumar D R, "Emission monitoring system using IOT", Dogo Rangsang Research Journal, UGC Care Group I Journal, ISSN: 347-7180, Vol 8 Issue-14, No.6, 2020.

- 14. Girish H, Shashikumar D R, "Display and misson computer software loading", International journal of engineering research & Technology (IJERT), ISSN: 2278-0181, Vol 10 Issue-08, No.13, August 2020.

- 15. Girish H, Shashikumar D R, "A Novel Optimization Framework for Controlling Stabilization Issue in Design Principle of FinFET based SRAM", International Journal of Electrical and Computer Engineering (IJECE) Vol. 9, No. 5 October 2019, pp. 4027~4034. ISSN: 2088-8708, DOI: 10.11591/ijece.v9i5.pp.4027-4034

- 16. Girish H, Shashikumar D R, "PAOD: a predictive approach for optimization of design in FinFET/SRAM", International Journal of Electrical and Computer Engineering (IJECE) Vol. 9, No. 2, April 2019, pp. 960~966. ISSN: 2088-8708, DOI: 10.11591/ijece.v9i2.pp.960-966

- 17. Girish H, Shashikumar D R, "SOPA: Search Optimization Based Predictive Approach for Design Optimization in FinFET/SRAM", © Springer International Publishing AG, part of Springer Nature 2019 Silhavy (Ed.): CSOC 2018, AISC 764, pp. 21–29, 2019. https://doi.org/10.1007/978-3-319-91189-2\_3.

- 18. Girish H, Shashikumar D R, "Cost-Effective Computational Modelling of Fault Tolerant Optimization of FinFET-based SRAM Cells", © Springer International Publishing AG 2017 R. Silhavy et al. (eds.), Cybernetics and Mathematics Applications in Intelligent Systems, Advances in Intelligent Systems and Computing 574, DOI 10.1007/978-3-319-57264-2\_1.

- 19. Girish H, Shashikumar D R, "A Survey on the Performance Analysis of FinFET SRAM Cells for Different

- Technologies", International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 8958, Volume-4 Issue-6, 2016.

- 20. Girish H, Shashikumar D R, "Insights of Performance Enhancement Techniques on FinFET-based SRAM Cells", Communications on Applied Electronics (CAE) ISSN: 2394-4714, Foundation of Computer Science FCS, New York, USA .Volume 5 No.6, July 2016 www.caeaccess.org

- 21. Girish H, Shashikumar D R, "DESIGN OF FINFET", International Journal of Engineering Research ISSN: 2319-6890) (online), 2347-5013(print) Volume No.5 Issue: Special 5, pp: 992-1128, doi: 10.17950/ijer/v5i5/013 2016.

- 22. Dr. MANGALA GOWRI S G, Dr. SHASHIDHAR T M, Dr. SUNITHA R, SHYLAJA V, Dr. GIRISH H, "DESIGN OF 3-BIT CMOS WALLACE MULTIPLIER", Seybold report, ISSN 1533-9211, Volume 18, Page No: 1260-1271 DOI: 10.5281/zenodo.8300481

- 23. Dr. Mangala Gowri S G, Dr. Girish H, Ramesh N, Dr. Nataraj Vijaypur, "IOT based plant monitoring system and smart irrigation using new features" ResMilitaris, vol.13, n°2, January Issue 2023 https://resmilitaris.net/menu-script/index.php/resmilitaris/article/view/3312/2608

- 24. Girish H.2023, Smart Theft Securityvehicular System Using Iot. Int J Recent Sci Res. 14(02), pp. 2881-2884. DOI: http://dx.doi.org/10.24327/ijrsr.2023.1402.0591

- 25. Dr. Mangala Gowri S G, Dr. Girish H, Dr. Santosh Dattatray Bhopale, Weed Detection based on Neural Networks, International Journal of All Research Education and Scientific Methods (IJARESM), ISSN: 2455-6211 Volume 11, Issue 3, March-2023, Impact Factor: 7.429, Available online at: www.ijaresm.com DOI: https://doi.org/11.56025/IJARESM.2023.11323351

- 26. Shashidhara, K.S., Girish, H., Parameshwara, M.C., Rai, B.K., Dakulagi, V. (2023). A Novel Approach for Identification of Healthy and Unhealthy Leaves Using Scale Invariant Feature Transform and Shading Histogram-PCA Techniques. In: Shetty, N.R., Patnaik, L.M., Prasad, N.H. (eds) Emerging Research in Computing, Information, Communication and Applications. Lecture Notes in Electrical Engineering, vol 928. Springer, Singapore. https://doi.org/10.1007/978-981-19-5482-5\_47